## **Premier Stereo DAC with 2Vrms Driver**

**Datasheet**

| Device | Description                                       | DNR<br>(dB) | Power Supply<br>(Output Level)   | No DC-blocking capacitor | Pop-Noise<br>Free | Package |

|--------|---------------------------------------------------|-------------|----------------------------------|--------------------------|-------------------|---------|

| ES9023 | Sabre Premier Stereo DAC with 2Vrms Op-Amp Driver | 112         | +3.6V (2Vrms)<br>+3.3V (1.9Vrms) | V                        | V                 | 16-SOP  |

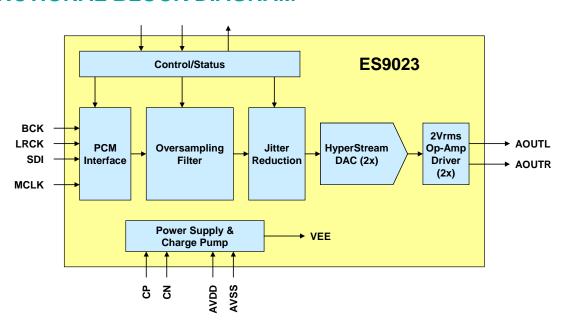

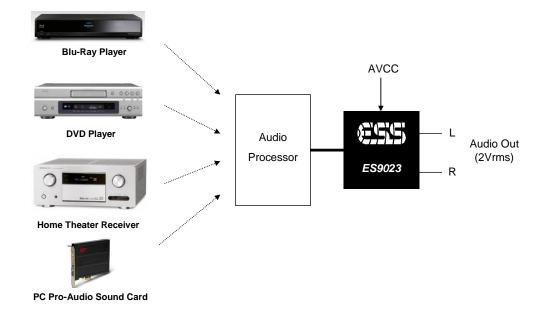

The ES9023 is a 24-bit stereo audio DAC with an integrated 2Vrms op-amp driver. Powered by the industry proven Sabre DAC technology, the ES9023 combines best-sounding audio with lowest system cost and highest performance into the ideal D/A converter for line-level output applications such as Blu-ray players, CD / DVD players, set-top boxes, digital TVs and audio receivers.

With patented HyperStream® architecture and Time Domain Jitter Eliminator, the ES9023 delivers jitter-free studio quality audio with 112dB DNR.

Using an integrated charge pump to generate the negative supply, the ES9023 can operate from a single AVCC supply to drive a ground-referenced 2Vrms output, eliminating the need for output dc-blocking capacitors. Optionally, the output level can be adjusted by using an external resistor, allowing for output level below 2Vrms. Pop-noise is eliminated through a comprehensive suppression on power up/down, mute, reset, loss of power or clock. Dedicated control/status pins allow easy system integration without the need for microcontroller programming.

| FEATURE                                                                                                        | BENEFIT                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sabre DAC and 2Vrms op-amp driver integration                                                                  | <ul> <li>Lowest system cost by minimizing external components</li> <li>Highest performance</li> <li>Best sounding audio – powered by Sabre DAC technology</li> </ul> |

| Patented HyperStream® and Jitter Elimination Architecture                                                      | <ul><li>Best dynamic range: 112dB</li><li>Immune to Clock Jitter</li></ul>                                                                                           |

| Adjustable output level                                                                                        | <ul> <li>Allow designer to customize output level (up to 2Vrms)<br/>based on application requirements via an external resistor</li> </ul>                            |

| Ground-referenced output                                                                                       | <ul> <li>Reduce cost by eliminating blocking capacitors</li> </ul>                                                                                                   |

| Pop-noise suppression                                                                                          | <ul> <li>Pop-free on power up/down, mute and reset</li> </ul>                                                                                                        |

| Dedicated control / status pins  I <sup>2</sup> S or left-justified select Soft-mute enable Zero-detect output | ■ Easy to use – no programming required                                                                                                                              |

| Charge pump for negative supply                                                                                | <ul> <li>Single AVCC simplifies power supply</li> </ul>                                                                                                              |

| Low power consumption in 16-SOP                                                                                | <ul> <li>Simple power supply to reduce PCB size</li> </ul>                                                                                                           |

## **FUNCTIONAL BLOCK DIAGRAM**

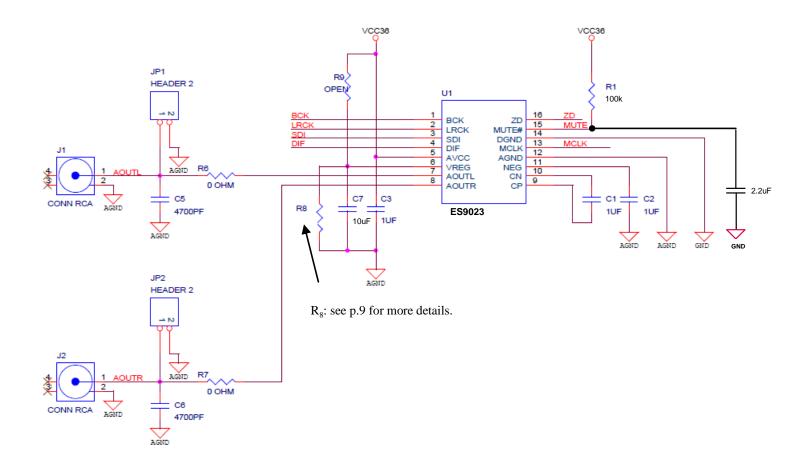

# **APPLICATION DIAGRAM**

August 26, 2022 0.72

## **ES9023 Datasheet**

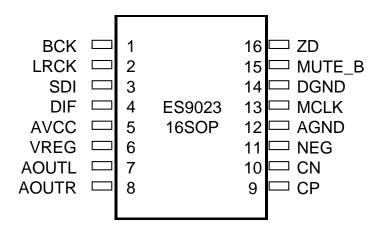

## **PIN LAYOUT**

## **PIN DESCRIPTIONS**

| Pin# | Name   | Type | Pin Description                                         |  |

|------|--------|------|---------------------------------------------------------|--|

| 1    | BCK    | I    | I <sup>2</sup> S Bit Clock                              |  |

| 2    | LRCK   | I    | I <sup>2</sup> S L/R (Word) Clock                       |  |

| 3    | SDI    | I    | I <sup>2</sup> S Serial Data Input                      |  |

| 4    | DIF    | I    | Input to select Left Justified or I <sup>2</sup> S data |  |

| 5    | AVCC   | Р    | AVCC Power supply                                       |  |

| 6    | VREG   | Р    | Analog Reference Output                                 |  |

| 7    | AOUTL  | 0    | Left Analog Output                                      |  |

| 8    | AOUTR  | 0    | Right Analog Output                                     |  |

| 9    | СР     | I    | Positive Terminal of External Charge Pump Capacitor     |  |

| 10   | CN     | I    | Negative Terminal of External Charge Pump Capacitor     |  |

| 11   | NEG    | Р    | Negative Power Supply (Internally Generated)            |  |

| 12   | AGND   | GND  | Analog Ground                                           |  |

| 13   | MCLK   | I    | Master (System) Clock                                   |  |

| 14   | DGND   | GND  | Digital Ground                                          |  |

| 15   | MUTE_B | I    | Active Low Mute Input                                   |  |

| 16   | ZD     | 0    | Zero Detect Output                                      |  |

## **FUNCTIONAL DESCRIPTION**

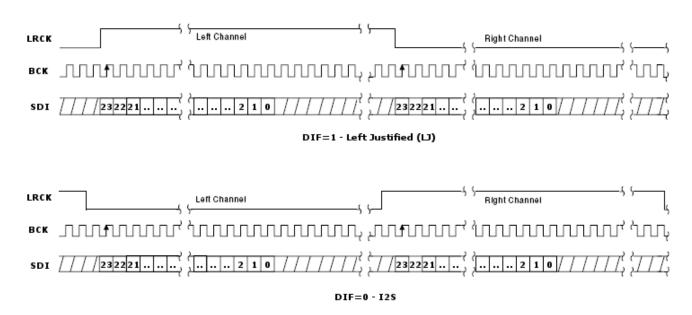

#### I2S Decoder

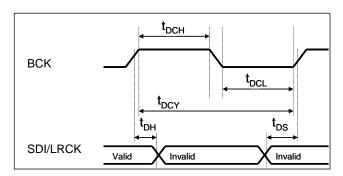

Run by the I²S bit clock, typically a 64 x FS clock, the I²S Decoder translates the incoming I²S data to 24-bit signed PCM data. If a smaller bit-width is used, the remaining is 'zero-padded'. Driving the DIF pin low will set the DAC in I²S mode while driving the pin high will set the DAC in LJ mode. Below is a timing diagram illustrating the two modes (LJ and I²S) utilized by the ES9023.

#### **Zero Detect**

The zero-detect function outputs an external status signal (ZD) based on a zero-valued input for a given number of clock cycles. The ZD output signal is set high when both data channels are zero for 8192 LRCK cycles.

#### **MCLK**

Asynchronous mode: MCLK must be > 192 x fs.

Synchronous mode: Please see table below for supported configurations.

| LRCK (kHz)   | MCLK (MHz)             |                        |                        |                        |                        |                        |                         |  |

|--------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|-------------------------|--|

| <u>fs</u>    | <u>128</u> x <u>fs</u> | <u>192</u> x <u>fs</u> | <u>256</u> x <u>fs</u> | <u>384</u> x <u>fs</u> | <u>512</u> x <u>fs</u> | <u>768</u> x <u>fs</u> | <u>1152</u> x <u>fs</u> |  |

| <u>32</u>    | -                      | -                      | -                      | 12.288                 | 16.384                 | 24.576                 | <u>36.864</u>           |  |

| <u>44.1</u>  | -                      | -                      | <u>11.2896</u>         | 16.9344                | 22.5792                | 33.8688                | _                       |  |

| <u>48</u>    | -                      | -                      | 12.288                 | 18.432                 | 24.576                 | <u>36.864</u>          | -                       |  |

| <u>88.2</u>  | <u>11.2896</u>         | 16.9344                | 22.5792                | 33.8688                | <u>45.1584</u>         | -                      | -                       |  |

| <u>96</u>    | 12.288                 | 18.432                 | 24.576                 | 36.864                 | 49.152                 | =                      | _                       |  |

| <u>176.4</u> | 22.5792                | 33.8688                | <u>45.1584</u>         | =                      |                        | -                      | -                       |  |

| <u>192</u>   | 24.576                 | 36.864                 | 49.152                 | =                      | =                      | =                      | _                       |  |

For best performance, 256 x fs or greater is recommended for 32kHz to 96kHz sampling.

August 26, 2022 0.72

### **ES9023 Datasheet**

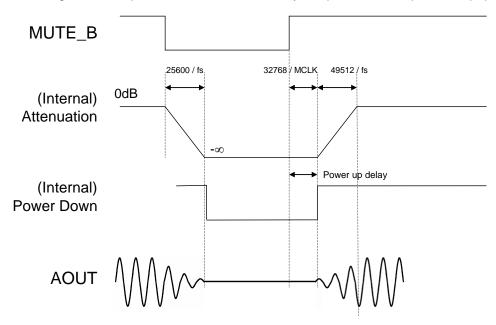

#### MUTE\_B Pin (Active Low)

This input pin provides the ability to slowly ramp down the audio volume, and then enter low power standby. Release of mute will cause the ES9023 to emerge from low power mode and then slowly ramp the audio to provide a pop free startup.

Activation/release of the MUTE\_B input pin initiates a sequence of internal events detailed below:

- On assertion of the MUTE B pin:

- The output signal will ramp to the -∞ level. The ramping takes 25600 / fs seconds, where fs = sampling rate in Hz.

- o After the output signal reaches the -∞ level, analog section is turned off and the ES9023 enters a low power standby state.

- On release of the MUTE\_B pin:

- The ES9023 emerges from low power standby, starts an internal counter and activates the analog section

- During the delay counter time, the internal charge pump and Vref stabilize.

- When the counter reaches 32768 MCLK cycles, the audio signal is applied and the volume is ramped over 49512 / fs seconds to maximum, where fs = sampling rate in Hz.

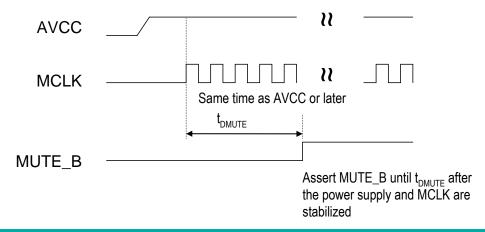

To minimize pop noise at power up, an external circuit should be used to hold the MUTE\_B pin asserted until t<sub>DMUTE</sub> (see p.10) after the power supply and MCLK are stabilized.

- This can be realized using a reset IC, an MCU GPIO pin (default to low at power-up and changed to high by software later), or an RC time delay on this pin.

- If MUTE\_B pin is released too early, pop noise may occur due to the ramp-up of internal voltage.

#### DAC / OP-AMP

Each HyperStream® DAC is followed by an op-amp circuit for each channel. A pop suppression circuit is added on the output to eliminate any "pop" noise that may be heard during muting, un-muting, power-up and power-down sequences. In some conditions, pop noise may be audible. See the MUTE B pin section above.

### **Charge Pump (Negative Voltage Generation)**

This is an analog circuit required to generate an internal negative supply. With positive and negative supplies, the op-amp circuits will be able to generate a ground-referenced 2Vrms output.

August 26, 2022 0.72

# **ES9023 Datasheet**

## **APPLICATION DIAGRAM**

## **ELECTRICAL SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                          | RATING                |

|------------------------------------|-----------------------|

| Storage temperature                | -65°C to +105°C       |

| Voltage range for 5V tolerant pins | -0.5V to +5.5V        |

| Voltage range for all other pins   | -0.5V to (AVCC+ 0.5V) |

**WARNING:** Stress beyond those listed under the Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions beyond those indicated in the Recommended Operating Conditions section of this specification is not implied. Exposure to the Absolute Maximum Ratings conditions for extended periods may affect device reliability.

WARNING: Electrostatic Discharge (ESD) can damage this device. Proper procedures must be followed to avoid ESD when handling this device.

#### RECOMMENDED OPERATING CONDITIONS

| PARAMETER             | SYMBOL | CONDITIONS                                                               |

|-----------------------|--------|--------------------------------------------------------------------------|

| Operating temperature | TA     | 0°C to 70°C                                                              |

| Power supply voltage  | AVCC   | +3.6V ±5%, 31mA nominal (Note 1), or<br>+3.3V ±5%, 23mA nominal (Note 1) |

#### Note

1) fs = 48kHz, MCLK = 27MHz,  $I^2S$  input, output unloaded

## DC ELECTRICAL CHARACTERISTICS

Table 1 DC Electrical Characteristics

| SYMBOL          | PARAMETER                 | MIN  | MAX        | UNIT | COMMENTS                                                    |

|-----------------|---------------------------|------|------------|------|-------------------------------------------------------------|

| ViH             | High-level input voltage  | 2    | AVCC       | V    | All inputs TTL levels except CLK and 5V tolerant input pins |

|                 |                           | 2    | 5.5        | V    | All 5V tolerant inputs                                      |

| VIL             | Low-level input voltage   | -0.3 | 0.8        | V    | All input TTL levels except CLK                             |

| Vclkh           | CLK high-level input      | 2    | AVCC+ 0.25 | V    | TTI level input                                             |

| Vclkl           | CLK low-level input       | -0.3 | 0.8        | V    | TTL level input                                             |

| Vон             | High-level output voltage | 3    |            | V    | Ioн = 1mA                                                   |

| V <sub>OL</sub> | Low-level-output voltage  |      | 0.45       | V    | I <sub>OL</sub> = 4mA                                       |

| I <sub>LI</sub> | Input leakage current     |      | ±15        | Α.   |                                                             |

| I <sub>LO</sub> | Output leakage current    |      | ±15        | μΑ   |                                                             |

| Cin             | Input capacitance         |      | 10         | ,r   | fc = 1MHz                                                   |

| Со              | Input/output capacitance  |      | 12         | pF   | IC = IIVIDZ                                                 |

| Cclk            | CLK capacitance           |      | 20         | pF   | fc = 1MHz                                                   |

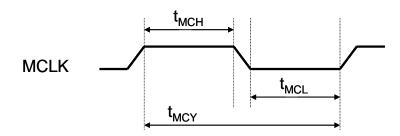

# **MCLK Timing**

| Parameter             | Symbol           | Min   | Max   | Unit |

|-----------------------|------------------|-------|-------|------|

| MCLK pulse width high | Тмсн             | 9     |       | ns   |

| MCLK pulse width low  | T <sub>MCL</sub> | 9     |       | ns   |

| MCLK cycle time       | T <sub>MCY</sub> | 20    |       | ns   |

| MCLK duty cycle       |                  | 45:55 | 55:45 |      |

# **Audio Interface Timing**

| Parameter                               | Symbol           | Min   | Max   | Unit |

|-----------------------------------------|------------------|-------|-------|------|

| BCK pulse width high                    | tосн             | 20    |       | ns   |

| BCK pulse width low                     | t <sub>DCL</sub> | 20    |       | ns   |

| BCK cycle time                          | t <sub>DCY</sub> | 44    |       | ns   |

| BCK duty cycle                          |                  | 45:55 | 55:45 |      |

| SDI/LRCK set-up time to BCK rising edge | t <sub>DS</sub>  | 2     |       | ns   |

| SDI/LRCK hold time to BCK rising edge   | t <sub>DH</sub>  | 2     |       | ns   |

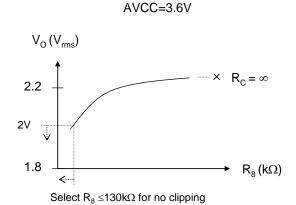

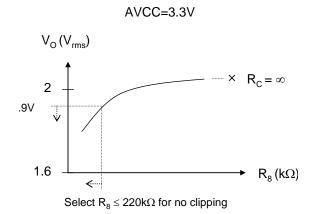

## **ANALOG PERFORMANCE**

#### **Test Conditions (unless otherwise stated)**

- 1.  $T_A = 25^{\circ}C,\ AVCC = +3.6V,\ fs = 44.1kHz,\ MCLK = 27MHz,\ 24-bit\ data,\ R_L \geq 10k\Omega,\ Signal\ Frequency = 1kHz$

- 2. SNR / DNR: A-weighted over 20Hz-22kHz in averaging mode

- 3. THD+N: un-weighted over 20Hz-22kHz bandwidth

| PARAMETER                 | SYMBOL         | CONDITIONS                         | MIN     | TYP     | MAX     | UNIT |

|---------------------------|----------------|------------------------------------|---------|---------|---------|------|

| PCM sampling rate         | f <sub>S</sub> |                                    |         |         | 200     | kHz  |

| Mute Delay                | tomute         |                                    | 500     |         |         | ms   |

| DYNAMIC PERFORMAN         | ICE            |                                    |         |         |         |      |

| DNR (A-weighted)          |                | -60dBFS                            |         | 112     |         | dB-A |

| THD+N                     |                | 0dBFS                              |         | 0.002   | 0.006   | %    |

| I HD+N                    |                | -3dBFS                             |         |         | 0.005   | %    |

| Interchannel Isolation    |                |                                    |         | 100     |         | dB   |

| DC Accuracy               |                |                                    |         |         |         |      |

| Absolute DC Offset        |                |                                    |         | < 4     |         | mV   |

| Output Valtage            | V              | 0dBFS, AVCC = +3.6V, $R_8$ = 130kΩ |         | 2.0     |         | Vrms |

| Output Voltage            | Vo             | 0dBFS, AVCC = +3.3V, $R_8$ = 220kΩ |         | 1.9     |         | Vrms |

| Load Resistance           | $R_L$          |                                    | 5       |         |         | kΩ   |

| Digital Filter Performand | ce             |                                    |         |         |         |      |

| Deer hand                 |                | ±0.005dB                           |         |         | 0.454fs | Hz   |

| Pass band                 |                | -3dB                               |         |         | 0.49fs  | Hz   |

| Stop band                 |                | < -115dB                           | 0.546fs |         |         | Hz   |

| Group Delay               |                |                                    |         | 35 / fs |         | s    |

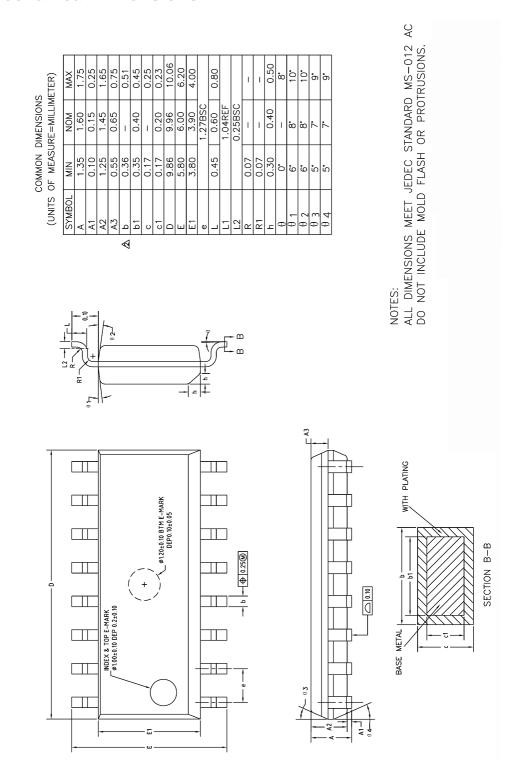

## **16-Pin SOP Mechanical Dimensions**

The solder paste and PCB finish/plating must be 100% lead-free in order to ensure proper solderability.

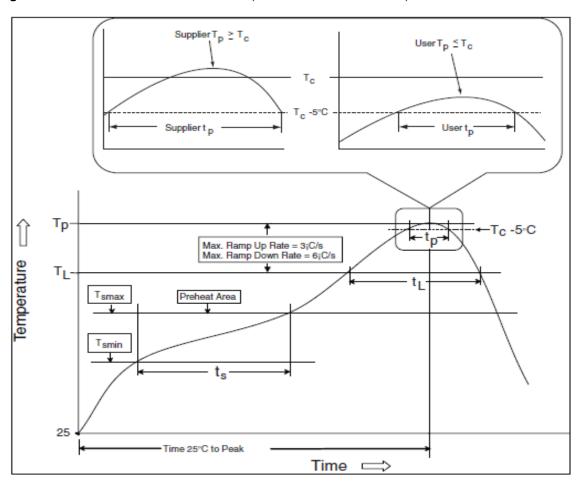

### **Reflow Process Considerations**

For lead-free soldering, the characterization and optimization of the reflow process is the most important factor you need to consider.

The lead-free alloy solder has a melting point of 217°C. This alloy requires a minimum reflow temperature of 235°C to ensure good wetting. The maximum reflow temperature is in the 245°C to 260°C range, depending on the package size (*Table RPC-2*). This narrows the process window for lead-free soldering to 10°C to 20°C.

The increase in peak reflow temperature in combination with the narrow process window makes the development of an optimal reflow profile a critical factor for ensuring a successful lead-free assembly process. The major factors contributing to the development of an optimal thermal profile are the size and weight of the assembly, the density of the components, the mix of large and small components, and the paste chemistry being used.

Reflow profiling needs to be performed by attaching calibrated thermocouples well adhered to the device as well as other critical locations on the board to ensure that all components are heated to temperatures above the minimum reflow temperatures and that smaller components do not exceed the maximum temperature limits (*Table RPC-2*).

To ensure that all packages can be successfully and reliably assembled, the reflow profiles studied and recommended by ESS are based on the JEDEC/IPC standard J-STD-020 revision D.1.

Figure RPC-1. IR/Convection Reflow Profile (IPC/JEDEC J-STD-020D.1)

#### Table RPC-1 Classification reflow profile

| Profile Feature                                                                          | Pb-Free Assembly                                                                                                                                                 |

|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preheat/Soak                                                                             |                                                                                                                                                                  |

| Temperature Min (Tsmin)                                                                  | 150°C                                                                                                                                                            |

| Temperature Max (Tsmax)                                                                  | 200°C                                                                                                                                                            |

| Time (ts) from (Tsmin to Tsmax)                                                          | 60-120 seconds                                                                                                                                                   |

| Ramp-up rate (TL to Tp)                                                                  | 3°C / second max.                                                                                                                                                |

| Liquidous temperature (TL)                                                               | 217°C                                                                                                                                                            |

| Time (tL) maintained above TL                                                            | 60-150 seconds                                                                                                                                                   |

| Peak package body temperature (Tp)                                                       | For users Tp must not exceed the Classification temperature in Table RPC-2. For suppliers Tp must equal or exceed the Classification temperature in Table RPC-2. |

| Time (tp)* within 5°C of the specified classification temperature (Tc), see Figure RPC-1 | 30* seconds                                                                                                                                                      |

| Ramp-down rate (Tp to TL)                                                                | °C / second max.                                                                                                                                                 |

| Time 25 °C to peak temperature                                                           | 8 minutes max.                                                                                                                                                   |

| * Tolerance for peak profile temperature (Tp) is defin                                   | ned as a supplier minimum and a user maximum.                                                                                                                    |

- Note 1: All temperatures refer to the center of the package, measured on the package body surface that is facing up during assembly reflow (e.g., live-bug). If parts are reflowed in other than the normal live-bug assembly reflow orientation (i.e., dead-bug), Tp shall be within ±2°C of the live-bug Tp and still meet the Tc requirements, otherwise, the profile shall be adjusted to achieve the latter. To accurately measure actual peak package body temperatures refer to JEP140 for recommended thermocouple use.

- Note 2: Reflow profiles in this document are for classification/preconditioning and are not meant to specify board assembly profiles. Actual board assembly profiles should be developed based on specific process needs and board designs and should not exceed the parameters in Table RPC-1. For example, if Tc is 260°C and time tp is 30 seconds, this means the following for the supplier and the user.

For a supplier: The peak temperature must be at least 260°C. The time above 255°C must be at least 30 seconds.

For a user: The peak temperature must not exceed 260°C. The time above 255°C must not exceed 30 seconds.

Note 3: All components in the test load shall meet the classification profile requirements.

#### Table RPC-2 Pb-Free Process – Classification Temperatures (Tc)

| Package Thickness | Volume mm3, <350 | Volume mm3, 350 to 2000 | Volume mm3, >2000 |

|-------------------|------------------|-------------------------|-------------------|

| <1.6 mm           | 260°C            | 260°C                   | 260°C             |

| 1.6 mm – 2.5 mm   | 260°C            | 250°C                   | 245°C             |

| >2.5 mm           | 250°C            | 245°C                   | 245°C             |

- **Note 1:** At the discretion of the device manufacturer, but not the board assembler/user, the maximum peak package body temperature (Tp) can exceed the values specified in Table RPC-2. The use of a higher Tp does not change the classification temperature (Tc).

- Note 2: Package volume excludes external terminals (e.g., balls, bumps, lands, leads) and/or non-integral heat sinks.

- Note 3: The maximum component temperature reached during reflow depends on package thickness and volume. The use of convection reflow processes reduces the thermal gradients between packages. However, thermal gradients due to differences in thermal mass of SMD packages may still exist.

## **ORDERING INFORMATION**

| Part Number | Description                                | Package |

|-------------|--------------------------------------------|---------|

| ES9023P     | Sabre Premier Stereo DAC with 2Vrms Driver | 16-SOP  |

The letter P at the end of the part number identifies the package type SOP.

### **REVISION HISTORY**

| Revision | Date               | Notes                                                         |

|----------|--------------------|---------------------------------------------------------------|

| 0.1      | September 17, 2010 | Initial version                                               |

| 0.2      | November 3, 2010   | Update Application Diagram                                    |

| 0.4      | October 29, 2013   | Update MUTE timing                                            |

| 0.5      | July 22, 2014      | Updated ESS' FAX number. Added medical liabilities disclaimer |

| 0.6      | January 22, 2015   | Cleaned up formatting and corrected typos                     |

| 0.7      | February 18, 2015  | Corrected filter formulae in the Analog Performance table     |

| 0.71     | April 6, 2015      | Updated HQ address and phone number                           |

| 0.72     | August 26, 2022    | Updated HQ address                                            |

ESS IC's are not intended, authorized, or warranted for use as components in military applications, medical devices or life support systems. ESS assumes no liability whatsoever and disclaims any expressed, implied or statutory warranty for use of ESS IC's in such unsuitable applications.

No part of this publication may be reproduced, stored in a retrieval system, transmitted, or translated in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without the prior written permission of ESS Technology, Inc. ESS Technology, Inc. makes no representations or warranties regarding the content of this document. All specifications are subject to change without prior notice. ESS Technology, Inc. assumes no responsibility for any errors contained herein. U.S. patents pending.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

ESS Technology:

ES9023P